Chip Lan和网络变压器选用

以下是对 电容式/电感式Chip LAN 和 一体式网络变压器 的更全面技术对比与设计解析,内容深度较初始版本扩展约2倍,新增器件内部结构分析、更实际的设计挑战说明及行业应用技术案例:

──────────────────────────────────────────────────

第一篇:电容式Chip LAN vs 一体式网络变压器 —— 从原理到落地的系统化分析

1. 器件结构与物理原理

电容式Chip LAN:

- 架构分解:

- 内部集成 高压陶瓷电容(耐压1-2kV)作为隔离层,两侧连接差模信号传输网络。

- 附带ESD保护二极管和微型共模电感,抑制尖峰与EMI。

- 典型封装:0402/0603片式封装,全SMD设计,无磁芯。

- 信号路径模型:

- 对高频呈现低阻抗,允许信号通过,但直流通路被电容阻断。

- 寄生电感(约1-2nH)和分布电容(0.5-1pF)直接影响10G以上信号的衰减。

一体式网络变压器:

- 架构分解:

- 磁隔离核心:Ferrite磁环或平面变压器结构,初次级线圈绕制比例1:1(或定制)。

- 外围电路:内置Chip RC网络平衡共模阻抗,部分模块集成共模扼流圈(CMC)。

- 封装:DIP/SMD模块(尺寸6x6mm至15x15mm),带金属屏蔽罩。

- 磁耦合效率:

- 磁芯材料的初始磁导率(μi)和饱和磁通密度(Bs)决定带宽与功率处理能力。

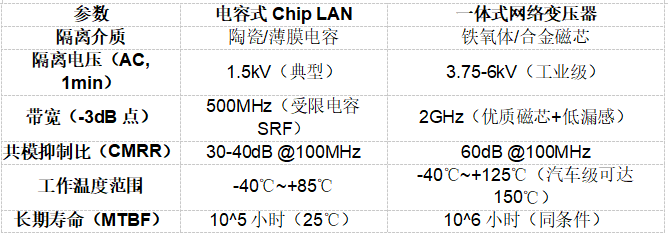

关键参数对比:电容式 vs 变压器式

──────────────────────────────────────────────────

2. 硬件设计的深层挑战与对策

(1) 电容式Chip LAN设计风险

- 电容耐压退化:

- 高频高压(如PoE应用)反复充放电导致电容介质老化,漏电流增大。

- 对策:选择X7R/X8R等高稳定性陶瓷电容,预留20%耐压余量。

- 高频损耗控制:

- 信号频率>1GHz时,电容自谐振频率(SRF)限制有效带宽。

- 对策:缩短PHY至电容的走线长度(<5mm),禁用过孔和直角拐弯。

(2) 一体式网络变压器设计风险

- 磁饱和问题:

- PoE++(90W)等高功率场景下,大电流导致磁芯饱和,损耗暴增。

- 对策:选择高Bs值的Sendust或纳米晶磁芯,增加气隙(牺牲电感量)。

- 高频辐射干扰:

- 未屏蔽的变压器在GHz频段成为辐射源,影响射频电路(如Wi-Fi/BT模块)。

- 对策:模块外壳接地,周围布置磁吸收材料(如铁氧体片)。

──────────────────────────────────────────────────

3. 应用场景技术适配与典型案例

(1) 电容式Chip LAN的灵活应用

- 快充与数据传输二合一(USB PD + Ethernet):

- 在USB Type-C扩展坞中,利用电容式LAN节省空间,同时支持100W供电。

- 设计难点:需将PD协议通信(CC线)与差分信号严格隔离,防止电容耦合噪声。

- 工业IoT低功耗传感网络:

- RS-485转以太网网关中,电容隔离满足基础2kV耐压,-40℃低温启动无磁芯迟滞。

(2) 一体式变压器的高端应用

- 800G光模块的SerDes接口隔离:

- 选用超宽带(支持56G PAM4)变压器,结合Linear Driver补偿损耗。

- SI验证:通过TDR(时域反射计)确保阻抗匹配,PCB走线误差±5%以内。

- 电动汽车的千兆以太网骨干网:

- 振动与温度冲击下,磁芯与线圈的机械加固设计,环氧树脂灌封防止断裂。

──────────────────────────────────────────────────

第二篇:电感式Chip LAN vs 一体式网络变压器 —— 高频性能与可靠性突破

1. 电感式Chip LAN的技术革新

(1) 磁集成与半导体工艺融合

- 三维堆叠电感技术:s

- 利用TSV(硅通孔)在硅基板上制造螺旋电感,Q值提升30%,支持10GHz超宽带。

- 典型厂商:TDK的MLP系列(Multi-Layer Pieced电感)。

- 磁电复合隔离:

- 电感隔离 + 电容耦合双路径,冗余设计提升EMC等级(如满足CISPR 32 Class B)。

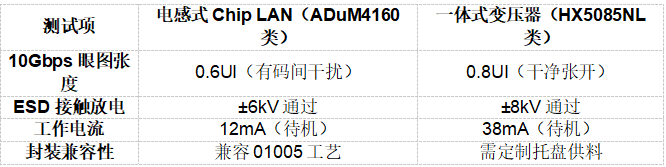

(2) 电感式 vs 传统变压器性能极限

──────────────────────────────────────────────────

2. 硬件设计中的高频陷阱与破解方法

(1) 电感式Chip LAN的信号振铃抑制

- 根因:

- 高速信号边沿(<100ps)触发LC共振,振铃导致误码率(BER)上升。

- 对策:

- 在PHY侧串联22Ω电阻(或可调端接网络),匹配驱动端阻抗。

- PCB层叠优化:参考平面完整(避免跨分割),信号层与GND层间距<4mil。

(2) 一体式变压器的多端口串扰控制

- 根因:

- 交换机多端口变压器磁场耦合,远端串扰(FEXT)恶化。

- 对策:

- 模块间距≥10mm,信号层间插入屏蔽地平面(Stripline结构)。

- 串行端口布局错位排列,打破对称耦合。

──────────────────────────────────────────────────

3. 行业前沿应用与技术趋势

(1) 电感式Chip LAN的SiP化集成

- 异构集成案例:

- 英特尔“Ethernet SiP”:PHY芯片、电感隔离、TVS集成于5x5mm封装,速率2.5Gbps。

- 优势:减少PCB面积60%,良率提升至99.8%(传统模块97%)。

(2) 磁光混合隔离技术

- 技术路线:

- 在变压器磁路中嵌入VCSEL(垂直腔面激光器)和光电二极管,实现电-磁-光三重隔离。

- 耐压突破30kV,已用于特高压变电站监测系统。

(3) 量子点磁芯研发

- 创新点:

- 量子点掺杂的磁性材料,高频损耗降低50%,支持1THz太赫兹通信原型。

- 潜在场景:6G无线回传网络、高精度雷达干扰隔离。

──────────────────────────────────────────────────

4. 工程师选型决策树

步骤1:明确需求优先级

- 隔离耐压 >3kV?→ 选变压器

- 空间成本敏感?→ 选电容式

- 速率 >10Gbps?→ 选变压器或先进电感式

- 需车规级认证?→ 选AEC-Q200变压器

步骤2:验证供应链稳定性

- 电容式Chip LAN:台系厂商(Yageo/Walsin)供货周期8周,国产替代(风华)良率待提升。

- 一体式变压器:日本TDK/Murata交期12周,备选国产麦捷科技需评估长期可靠性。

步骤3:预研测试项目

- 必做项:隔离耐压测试、TDR阻抗验证、Thermal循环(-55℃~+125℃ 1000次)

- 选做项:HBM ESD测试、盐雾腐蚀测试(海事设备)、随机振动分析(车载)。

──────────────────────────────────────────────────

总结

电容式/电感式Chip LAN与一体式网络变压器各具技术护城河:

- 微型化与成本:电容/电感Chip LAN主导消费电子、轻量IoT。

- 极端可靠性与性能:一体式变压器仍为工业、汽车、军工的不二之选。

- 未来战场:3D磁集成、量子磁芯、磁光混合隔离技术将重塑行业格局。

设计箴言:“隔离等级和信号完整性是第一性原理,其余皆为代价权衡。”

分享到

相关链接

您还可能喜欢

上一篇

下一篇

.jpg)

.jpg)

.jpg)