以太网电路设计指南

一、以太网接口硬件架构概览

典型以太网硬件接口主要由以下几大部分组成:

- CPU/MCU:主控系统,负责上层协议处理。

- MAC(Media Access Control):媒体访问控制层,处理数据帧的封装与校验。

- PHY(Physical Layer):物理层接口,将MAC输出的数字信号转换为模拟电信号。

- 网络变压器(Magnetics):提供信号隔离、抗共模干扰和阻抗匹配功能。

- RJ45接口:物理连接点,实现与以太网物理介质的连接。

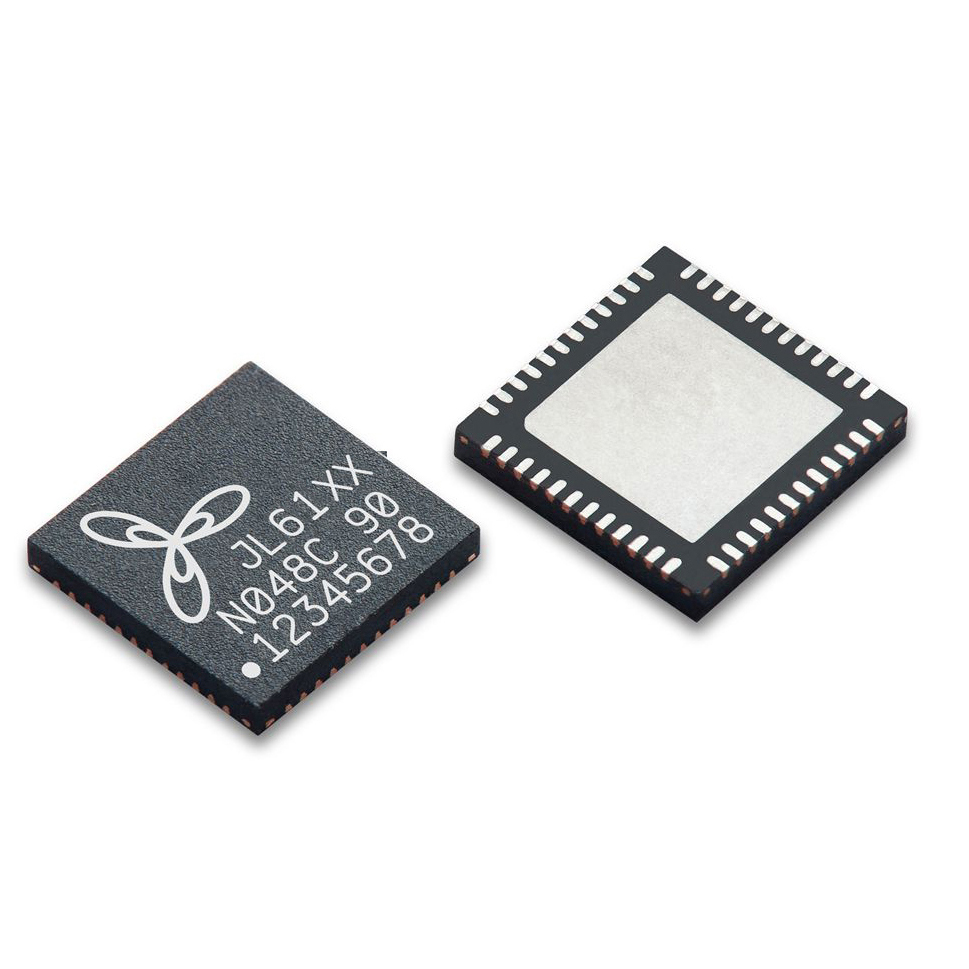

随着集成度提高,越来越多SoC(System on Chip)芯片已集成MAC,甚至部分集成了PHY,设计方式也在不断优化。

二、关键元件解析

(一)PHY芯片

- 作用:将MAC层的数字信号转换为适合网线传输的模拟信号。

- 关键参数:

- 速率:10/100Mbps(百兆)、1000Mbps(千兆)。

- 接口类型:MII/RMII/GMII(与MAC通信)。

- 传输距离:千兆以太网支持最长100米的双绞线传输。

- 特殊功能:部分PHY芯片支持POE(以太网供电)。

(二)网络变压器

- 作用:

- 电气隔离:阻断PHY与RJ45之间的直流分量,保护芯片。

- 抑制共模干扰:减少外部电磁干扰(EMI)。

- 阻抗匹配:优化信号传输质量。

(三)RJ45接口

- 百兆(100BASE-TX):仅使用2对(4芯)双绞线(Cat5或更高规格电缆中的1-2、3-6线对),1对用于发送数据,1对用于接收数据,其余2对未使用。

- 千兆(1000BASE-T):使用全部4对(8芯)双绞线(Cat5e或更高)。

三、PCB设计要点

(一)整体布局

- 尽量靠近RJ45,缩短差分走线长度。

- 下方避免其他信号线,防止干扰。

(二)差分线(TX/RX)走线规则

- 等长匹配(要求长度差≤5mil)。

- 阻抗控制(通常100Ω差分阻抗)。

- 避免锐角走线,减少信号反射。

(三)网口与变压器PCB设计要点

- 耐压隔离:网络变压器中间隔离区需足够宽,确保耐压要求。PHY与RJ45需分属不同地平面,禁止跨平面布局或走线。

- 抗干扰处理:变压器下方所有层挖空,避免底层铜箔引入噪声。

- 差分线布线:优先走底层,远离网口外壳接地层。阻抗建议控制在100Ω±10%(非强制但推荐)。

- 外壳接地:网口金属外壳接地线需加粗,确保低阻抗连接。

四、接口防护设计

- ESD保护器件:用于防止静电放电对后级电路造成损坏。

- 浪涌保护器件:用于防止雷击等产生的浪涌电压对电路造成损坏。

五、实际应用案例分析

以某工业自动化设备为例,其以太网接口设计采用了集成MAC和PHY的SoC芯片,通过合理布局和走线,实现了稳定可靠的通信。在实际应用中,该设备能够在复杂的电磁环境下稳定工作,满足了工业自动化对以太网通信的高要求。

分享到

相关链接

您还可能喜欢

上一篇

下一篇

.jpg)

.jpg)

.jpg)